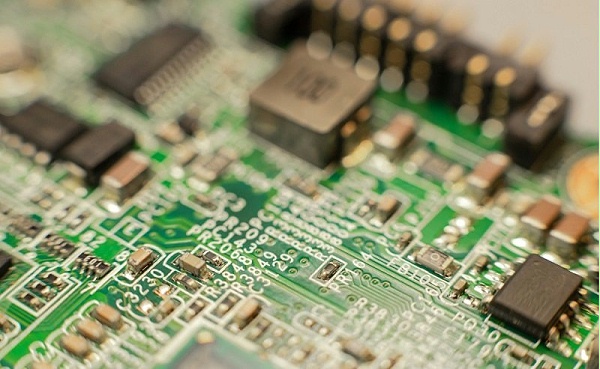

单片机控制板pcb设计流程:

1、元器件布局

在元器件的布局方面,应该把相互有关的元件尽量放得靠近一些,例如,时钟发生器、晶振、CPU的时钟输入端都容易产生噪声,在放置的时候应把它们靠近些。

对于那些容易产生噪声的器件、小电流电路、大电流电路开关电路等,应尽量使其远离单片机的逻辑控制电路和存储电路(ROM、RAM),如果可能的话,可以将这些电路另外制成电路板,这样有利于抗干扰,提高电路工作的可靠性。

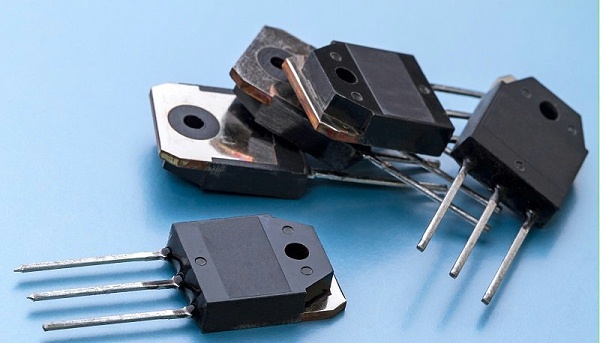

2、去耦电容

尽量在关键元件,如ROM、RAM等芯片旁边安装去耦电容。

实际上,印制电路板走线、引脚连线和接线等都可能含有较大的电感效应。

大的电感可能会在Vcc 走线上引起严重的开关噪声尖峰。

防止Vcc走线上开关噪声尖峰的唯一方法,是在VCC与电源地之间安放一个0.1uF的电子去耦电容。

如果电路板上使用的是表面贴装元件,可以用片状电容直接紧靠着元件,在Vcc引脚上固定。

最好是使用瓷片电容,这是因为这种电容具有较低的静电损耗(ESL)和高频阻抗,另外这种电容温度和时间上的介质稳定性也很不错。

尽量不要使用钽电容,因为在高频下它的阻抗较高。

在安放去耦电容时需要注意以下几点:

①在印制电路板的电源输入端跨接100uF左右的电解电容,如果体积允许的话,电容量大一些则更好。

②原则上每个集成电路芯片的旁边都需要放置一个0.01uF的瓷片电容,如果电路板的空隙太小而放置不下时,可以每 10个芯片左右放置一个1~10的钽电容。

③对于抗干扰能力弱、关断时电流变化大的元件和RAM、ROM 等存储元件,应该在电源线(Vcc)和地线之间接入去耦电容。

④电容的引线不要太长,特别是高频旁路电容不能带引线。

3、地线设计

在单片机控制系统中,地线的种类有很多,有系统地、屏蔽地、逻辑地、模拟地等,地线是否布局合理,将决定电路板的抗干扰能力。

在设计地线和接地点的时候,应该考虑以下问题:

逻辑地和模拟地要分开布线,不能合用,将它们各自的地线分别与相应的电源地线相连。

在设计时,模拟地线应尽量加粗,而且尽量加大引出端的接地面积。

一般来讲,对于输入输出的模拟信号,与单片机电路之间最好通过光耦进行隔离。

在设计逻辑电路的印制电路版时,其地线应构成闭环形式,提高电路的抗干扰能力。

地线应尽量的粗。如果地线很细的话,则地线电阻将会较大,造成接地电位随电流的变化而变化,致使信号电平不稳,导致电路的抗干扰能力下降。

在布线空间允许的情况下,要保证主要地线的宽度至少在2~3mm以上,元件引脚上的接地线应该在1.5mm左右。

要注意接地点的选择。当电路板上信号频率低于1MHz时,由于布线和元件之间的电磁感应影响很小,而接地电路形成的环流对干扰的影响较大,所以要采用一点接地,使其不形成回路。

当电路板上信号频率高于10MHz时,由于布线的电感效应明显,地线阻抗变得很大,此时接地电路形成的环流就不再是主要的问题了。所以应采用多点接地,尽量降低地线阻抗。

以上就是关于单片机控制板pcb设计流程的全部内容分享,如果您有单片机或者方案开发需求,可以点击右边的咨询热线和微信扫一扫直接和我们联系,宇凡微提供8/32位单片机,为客户量身定制的合封单片机,拥有成熟的封装技术和封装工艺,除了能够保证合封之后的良率以及安全性,还能根据客户的功能需求选择最佳的合封方式,节省成本。

免责声明:部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递 更多信息之 目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者在及时联系本站,我们 会尽快处理。官方所有内容、图片如未经过授权,禁止任何形式的采集、镜像,否则后果自负!

标题: 宇凡微

地址:https://www.yufanwei.com/