产品概述Product overview

YF8A050D是以EPROM作為记忆体的8位元微控制器,专為多IO產品的应用而设计,例如遥控器、风扇/灯光控制或是游乐器周边等等。採用CMOS製程并同时提供客户低成本、高性能等显著优势。YF8A050D核心建立在RISC精简指令集架构可以很容易地做编辑和控制,共有55条指令。除了少数指令需要2个时序,大多数指令都是1个时序即能完成,可以让使用者轻鬆地以程式控制完成不同的应用。因此非常适合各种低记忆容量但又复杂的应用。

在I/O的资源方面,YF8A050D有6根弹性的双向I/O脚,每个I/O脚都有单独的暂存器控制為输入或输出脚。而且每一个I/O脚位都有附加的程式控制功能如上拉或下拉电阻或开漏极(Open-Drain) 输出。

YF8A050D有一组计时器,可用系统频率当作一般的计时的应用或者从外部讯号触发来计数。

YF8A050D採用双时鐘机制,高速振盪或者低速振盪都由内部RC振盪输入。在双时鐘机制下,YF8A050D可选择多种工作模式如正常模式(Normal)、慢速模式(Slow mode)、待机模式(Standby mode) 与睡眠模式(Halt mode)可节省电力消耗延长电池寿命。

在省电的模式下,如待机模式(Standby mode)与睡眠模式(Halt mode)中,有多个中断源可以触发来唤醒 YF8A051D进入正常操作模式(Normal mode)或慢速模式(Slow mode)来处理突发事件。

功能特点Functional characteristics

-

宽广的工作电压:(指令时钟为 4 个CPU时钟,亦即 4T模式);2.0V ~ 5.5V @系统时钟≦8MHz;2.2V ~ 5.5V @系统时钟>8MHz。

-

宽广的工作温度:-40°C ~ 85°C;1Kx14 位的程序存储器空间;48字节的通用数据寄存器空间。

-

6 根可分别单独控制输入输出方向的I/O脚(GPIO)、PB[5:0];PB[3:0]可选择输入时使用内部下拉电阻

-

PB[5:4]及PB[2:0]可选择内部上拉电阻或开漏输出(Open-Drain);PB[3]可选择当作输入或开漏输出(Open-Drain)

-

8级深度硬件堆栈(Stack);存取数据有直接或间接寻址模式

-

一组8位上数定时器(Timer0)包含可编程的预分频器

-

一组8位下数定时器(Timer1)可选自动重载与连续下数计时

-

一个8位的脉冲宽度调变输出(PWM1);一个蜂鸣器输出(BZ1)

-

38/57KHz红外线载波(IR)频率可供选择,同时载波之极性也可以通过寄存器选择

-

内置上电复位电路(POR);内置低压复位功能(LVR)

-

内置看门狗计时(WDT),可由配置字节(Configuration Word)控制开关;

-

双时钟机制,系统时钟可以随时切换高速振荡或者低速振荡。高速振荡时钟:I_HRC (内部 1~20MHz高速RC振荡);低速振荡时钟:I_LRC (内部 32KHz低速RC振荡)

-

四种工作模式可随系统需求调整电流消耗:正常模式(Normal mode)、慢速模式(Slow mode)、待机模式(Standby mode)与睡眠模式(Halt mode)

-

五种硬件中断:Timer0 上溢中断、Timer1 下溢中断、WDT中断、PB输入状态改变中断、外部中断

-

YF8A050D在待机模式(Standby mode)下的五种唤醒中断:Timer0 上溢中断、Timer1 下溢中断、WDT中断、PB输入状态改变中断、外部中断

-

YF8A050D在睡眠模式(Halt mode)下的三种唤醒中断:WDT中断、PB输入状态改变中断、外部中断

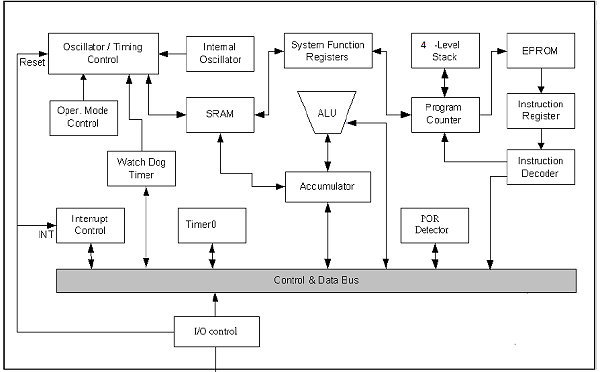

功能框图Functional block diagram

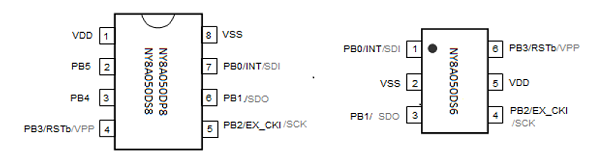

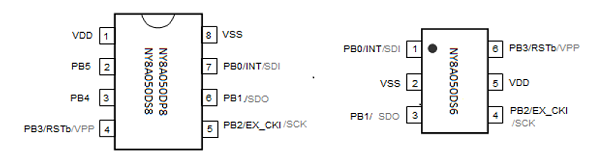

引脚排列图Pin layout

-

引脚图

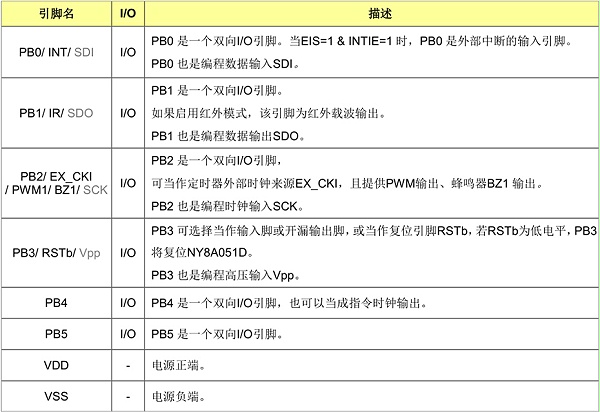

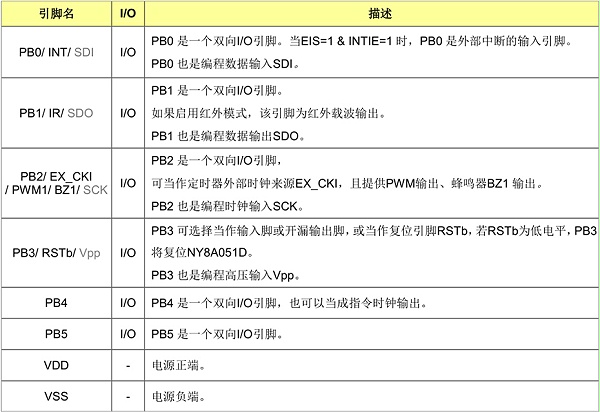

引脚说明Pin description

-

YF8A050D引脚说明

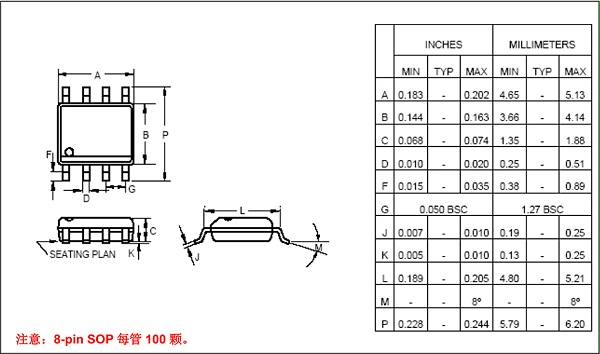

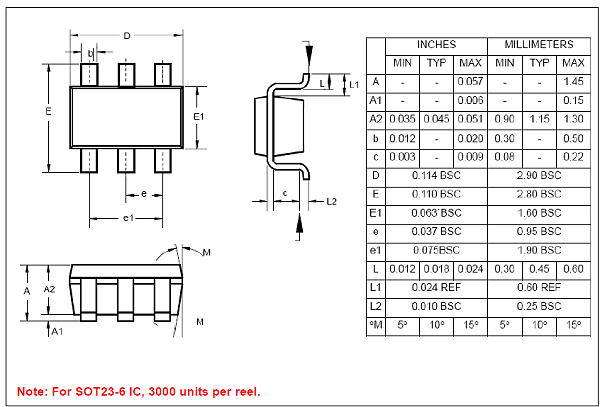

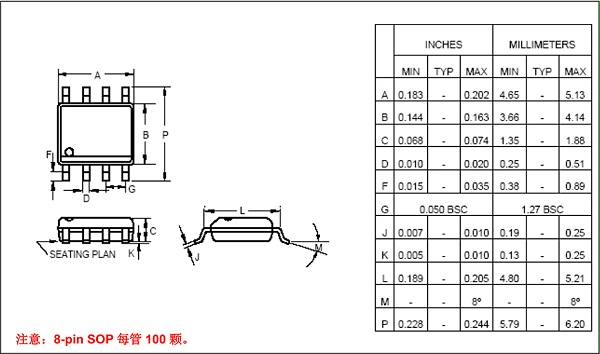

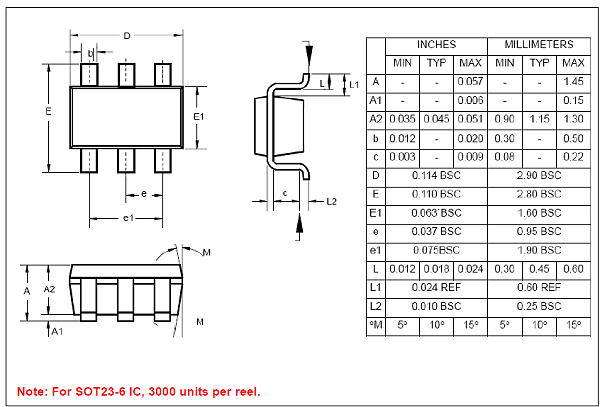

封装尺寸Package size

-

6引脚SOT23-6(63毫寸)

8引脚SOP(150毫寸)